# INTEGRATED CIRCUITS

# DATA SHEET

# **SA8026**

2.5GHz low voltage fractional—N dual frequency synthesizer

Preliminary specification Supersedes data of 1998 Apr 06

# 2.5GHz low voltage fractional-N dual synthesizer

**SA8026**

#### **FEATURES**

- Low phase noise

- Low power

- Fully programmable main and auxiliary dividers

- NORMAL & INTEGRAL charge pumps outputs

- Fast Locking Adaptive mode design

- Internal fractional spurious compensation

- Hardware and software power down

### **APPLICATIONS**

- 800 to 2500 MHz wireless equipment

- PCS

- Cellular phones

- WLAN

- Portable battery-powered radio equipment.

### **General description**

The SA8026 BICMOS device integrates programmable dividers, charge pumps and a phase comparator to implement a phase-locked loop. The device is designed to operate from 3 NiCd cells, in pocket phones, with low current and nominal 3 V supplies.

The synthesizer operates at VCO input frequencies up to 2.5 GHz. The synthesizer has fully programmable main, auxiliary and reference dividers. All divider ratios are supplied via a 3-wire serial programming bus.

Separate power and ground pins are provided to the analog and digital circuits. The ground leads should be externally short-circuited to prevent large currents flowing across the die and thus causing damage.  $V_{DDCP}$  could be greater than or equal to  $V_{DD}$ .

The charge pump current (gain) is fixed by an external resistance at pin Rset (pin). Only passive loop filters are used; the charge-pump operates within a wide voltage compliance range to provide a wider tuning range.

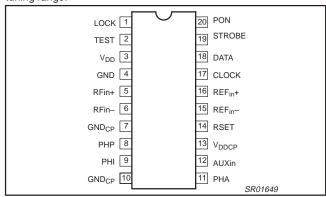

Figure 1. Pin Configuration

## **QUICK REFERENCE DATA**

| SYMBOL                             | PARAMETER                               | CONDITIONS            | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|-----------------------------------------|-----------------------|------|------|------|------|

| $V_{DD}$                           | Supply voltage                          | V <sub>DD</sub>       | 2.7  | _    | 5.5  | V    |

| V <sub>DDCP</sub>                  | Analog supply voltage                   | $V_{DDCP} \ge V_{DD}$ | 2.7  | _    | 5.5  | V    |

| I <sub>DDCP</sub> +I <sub>DD</sub> | Supply current                          | Main and Aux. on      | _    | 10.0 | 11.8 | mA   |

| I <sub>DDCP</sub> +I <sub>DD</sub> | Total supply current in power-down mode |                       | _    | 1    | _    | μΑ   |

| f <sub>VCO</sub>                   | Input frequency                         |                       | 800  | _    | 2500 | MHz  |

| f <sub>AUX</sub>                   | Input frequency                         |                       | 10   | _    | 550  | MHz  |

| f <sub>REF</sub>                   | Crystal reference input frequency       |                       | 10   | _    | 40   | MHz  |

| f <sub>PC</sub>                    | Maximum phase comparator frequency      |                       | _    |      | 4    | MHz  |

| T <sub>amb</sub>                   | Operating ambient temperature           |                       | -40  | _    | +85  | °C   |

## **ORDERING INFORMATION**

| TYPE NUMBER  | PACKAGE | PACKAGE                                                                |          |  |  |  |  |  |  |  |

|--------------|---------|------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

| I THE NOWBER | NAME    | DESCRIPTION                                                            | VERSION  |  |  |  |  |  |  |  |

| SA8026DH     | TSSOP20 | Plastic thin shrink small outline package; 20 leads; body width 4.4 mm | SOT360-1 |  |  |  |  |  |  |  |

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

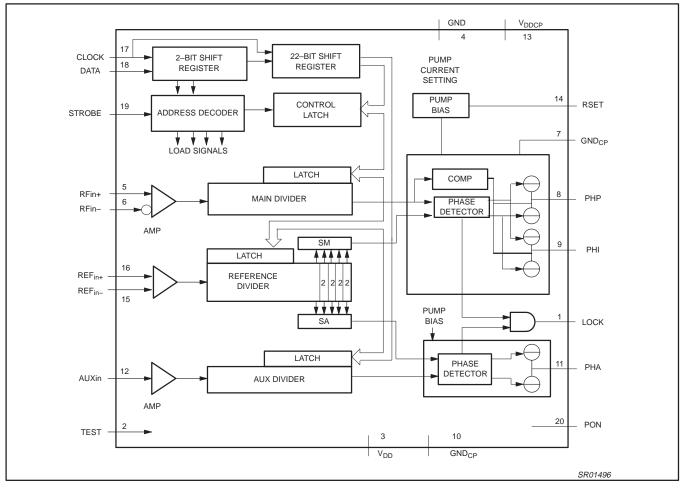

Figure 2. Block Diagram

# **PINNING**

| SYMBOL            | PIN | DESCRIPTION                       |

|-------------------|-----|-----------------------------------|

| LOCK              | 1   | Lock detect output                |

| TEST              | 2   | Test                              |

| $V_{DD}$          | 3   | Digital supply                    |

| GND               | 4   | Digital ground                    |

| RFin+             | 5   | RF positive input to main divider |

| RFin-             | 6   | RF negative input to main divider |

| GND <sub>CP</sub> | 7   | Charge pump ground                |

| PHP               | 8   | Main NORMAL chargepump            |

| PHI               | 9   | Main INTEGRAL chargepump          |

| GND <sub>CP</sub> | 10  | Charge Pump Ground                |

| SYMBOL             | PIN | DESCRIPTION                                                           |

|--------------------|-----|-----------------------------------------------------------------------|

| PHA                | 11  | Auxiliary chargepump output                                           |

| AUXin              | 12  | Input to auxiliary divider                                            |

| $V_{DDCP}$         | 13  | Charge pump supply voltage                                            |

| RSET 14            |     | External resistor from this pin to ground sets the chargepump current |

| REF <sub>in</sub>  | 15  | Reference input                                                       |

| REF <sub>in+</sub> | 16  | Reference input                                                       |

| CLOCK              | 17  | Programming bus clock input                                           |

| DATA               | 18  | Programming bus data input                                            |

| STROBE             | 19  | Programming bus enable input                                          |

| PON                | 20  | Power down control                                                    |

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

# **CHARACTERISTICS**

$V_{DDCP} = V_{DD} = +3.0V$ ,  $T_A = +25^{\circ}C$ ; unless otherwise specified.

| SYMBOL                 | PARAMETER                                         | CONDITIONS                                     | MIN.       | TYP. | MAX.  | UNIT |

|------------------------|---------------------------------------------------|------------------------------------------------|------------|------|-------|------|

| Supply; pin            | s 3, 13                                           | '                                              |            | •    | •     |      |

| V <sub>DD</sub>        | Digital supply voltage                            |                                                | 2.7        | _    | 5.5   | V    |

| V <sub>DDCP</sub>      | Analog supply voltage                             | $V_{DDCP} \ge V_{DD}$                          | 2.7        | _    | 5.5   | V    |

| I <sub>DDTotal</sub>   | Synthesizer operational digital supply current    | $V_{DD} = +3.0V$ (with main and aux on)        | -          | 10.0 | 11.8  | mA   |

| I <sub>standby</sub>   | Total supply current in power-down mode           | logic levels 0 or VDD                          | _          | 1    | -     | μА   |

| RFin main o            | livider input; pins 5, 6                          |                                                |            | •    |       | •    |

| f <sub>VCO</sub>       | VCO input frequency                               |                                                | 800        | _    | 2500  | MHz  |

| V <sub>RFin(rms)</sub> | AC-coupled input signal level                     | $R_s = 50 \Omega$ ; MAX. limit is indicative   | -18        | -    | 0     | dBm  |

| Z <sub>IRFin</sub>     | Input impedance (real part)                       | f <sub>VCO</sub> = 2.0 GHz                     | _          | TBD  | _     | kΩ   |

| C <sub>IRFin</sub>     | Typical pin input capacitance                     | indicative, not tested                         | _          | TBD  | _     | pF   |

| N <sub>m</sub>         | Main divider ratio                                |                                                | 512        | _    | 65535 |      |

| f <sub>PCmax</sub>     | Maximum loop comparison frequency                 | indicative, not tested                         | _          | _    | 4     | MHz  |

| AUX referer            | nce divider input; pins 12                        |                                                |            |      |       |      |

| f <sub>AUXin</sub>     | Input frequency range                             |                                                | 10         | _    | 550   | MHz  |

| V <sub>AUXin</sub>     | AC-coupled input signal level                     | $R_s = 50\Omega$ ; MAX. limit is indicative    | -18        | _    | 0     | dBm  |

|                        |                                                   |                                                | 80         | -    | 636   | mVpp |

| Z <sub>AUXin</sub>     | Input impedance (real part)                       | f <sub>VCO</sub> = 500 MHZ                     |            | TBD  | _     | kΩ   |

| C <sub>AUXin</sub>     | Typical pin input capacitance                     | indicative, not tested                         | -          | TBD  | 40004 | pF   |

| N <sub>AUX</sub>       | Auxiliary division ratio                          |                                                | 128        | _    | 16384 |      |

|                        | livider input; pins 15, 16                        |                                                |            |      |       | T    |

| f <sub>REFin</sub>     | Input frequency range from crystal                |                                                | 10         | -    | 40    | MHz  |

| VRFin                  | AC-coupled input signal level                     | $R_S = 50\Omega$ ; MAX. limit is indicative    | 360        | _    | 1300  | mVpp |

| Z <sub>REFin</sub>     | Input impedance (real part)                       |                                                | _          | TBD  | -     | kΩ   |

| C <sub>REFin</sub>     | Typical pin input capacitance                     | indicative, not tested                         | _          | TBD  | -     | pF   |

| R <sub>REF</sub>       | Reference division ratio                          | SA = SM = "000"                                | 4          | _    | 1023  |      |

| Charge pun             | np current setting resistor input; pin 14         |                                                |            | _    |       |      |

| R <sub>SET</sub>       | External resistor from pin 3 to ground            |                                                | 6          | 7.5  | 24    | kΩ   |

| V <sub>SET</sub>       | Regulated voltage at pin 3                        | $R_{SET} = 7.5 \text{ k}\Omega$                | -          | 1.25 | _     | V    |

| Charge pun             | np outputs (including fractional compensation pum | p); pins 8, 9, 11; R <sub>SET</sub> = 7.5 KΩ   | 2, FC = 80 |      |       |      |

| Icp                    | Chargepump current ratio to Iset                  | CURRENT GAIN I <sub>PH</sub> /I <sub>SET</sub> | -15        |      | +15   | %    |

| I <sub>MATCH</sub>     | Sink-to-source current matching                   | $V_{ph} = 1/2 V_{DDCP}$                        | -10        |      | +10   | %    |

| I <sub>ZOUT</sub>      | Output current variation versus Vph <sup>2</sup>  | V <sub>ph</sub> in compliance range            | -10        |      | +10   | %    |

| I <sub>LPH</sub>       | Charge pump off leakage current                   | $V_{cp} = 1/2 V_{DDCP}$                        | -10        |      | +10   | nA   |

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

# **CHARACTERISTICS (CONTINUED)**

| SYMBOL                                                          | PARAMETER                                                                                 | CONDITIONS                                                   | MIN.                 | TYP. | MAX.                   | UNIT      |  |  |  |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------|------|------------------------|-----------|--|--|--|--|--|

| $V_{ph}$                                                        | Charge pump voltage compliance                                                            |                                                              | 0.7                  | _    | V <sub>DDCP</sub> -0.8 | V         |  |  |  |  |  |

| Phase noise                                                     |                                                                                           |                                                              |                      |      |                        |           |  |  |  |  |  |

| C/N                                                             | Synthesizer's contribution to close-in-phase noise of 2100 MHz RF signal at 1 kHz offset. | fref = 19.44MHz;<br>fcomp = 240kHz<br>indicative, not tested | -                    | -75  | -                      | dBc<br>Hz |  |  |  |  |  |

| Interface logic input signal levels; pins 3, 15, 16, 18, 19, 20 |                                                                                           |                                                              |                      |      |                        |           |  |  |  |  |  |

| V <sub>IH</sub>                                                 | HIGH level input voltage                                                                  |                                                              | 0.7*V <sub>DD</sub>  | _    | V <sub>DD</sub> +0.3   | V         |  |  |  |  |  |

| V <sub>IL</sub>                                                 | LOW level input voltage                                                                   |                                                              | -0.3                 | -    | 0.3*V <sub>DD</sub>    | V         |  |  |  |  |  |

| I <sub>bias</sub>                                               | Input bias current                                                                        | logic 1 or logic 0                                           | <b>-</b> 5           | _    | +5                     | μΑ        |  |  |  |  |  |

| Lock detect                                                     | output signal (in push/pull mode); pin 1                                                  |                                                              |                      |      |                        |           |  |  |  |  |  |

| V <sub>OL</sub>                                                 | LOW level output voltage                                                                  | I <sub>sink</sub> = 2mA                                      | _                    | _    | 0.4                    | V         |  |  |  |  |  |

| V <sub>OH</sub>                                                 | HIGH level output voltage                                                                 | I <sub>source</sub> = -2mA                                   | V <sub>DD</sub> -0.4 | _    | _                      | V         |  |  |  |  |  |

# NOTES:

1.  $I_{SET} = \frac{V_{SET}}{R_{SET}}$  bias current for charge pumps.

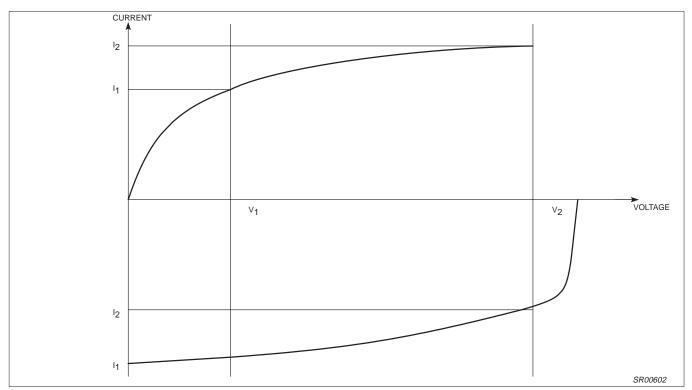

2. The relative output current variation is defined thus:

$$\frac{\Delta I_{OUT}}{I_{OUT}} = 2 \cdot \frac{(I_2 - I_1)}{I(I_2 + I_1)I}; \text{ with V}_1 = 0.7 \text{V}, \text{ V}_2 = \text{V}_{DDCP} - 0.8 \text{V (See Figure 3.)}$$

Figure 3. Relative Output Current Variation

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

# **Limiting values**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                     | PARAMETER                                                                                                  | MIN.        | MAX.                    | UNIT |

|----------------------------|------------------------------------------------------------------------------------------------------------|-------------|-------------------------|------|

| V <sub>DD</sub>            | Digital supply voltage                                                                                     | -0.3        | +5.5                    | V    |

| V <sub>DDCP</sub>          | Analog supply voltage                                                                                      | -0.3        | +5.5                    | V    |

| $\Delta V_{DDCP} - V_{DD}$ | Difference in voltage between V <sub>DDCP</sub> and V <sub>DD</sub> (V <sub>DDCP</sub> ≥ V <sub>DD</sub> ) | -0.3        | +2.8                    | V    |

| V <sub>n</sub>             | Voltage at pins 1, 2, 5, 6, 12, 15 to 20                                                                   | -0.3        | V <sub>DD</sub> + 0.3   | V    |

| V <sub>1</sub>             | Voltage at pin 8, 9, 13                                                                                    | -0.3        | V <sub>DDCP</sub> + 0.3 | V    |

| $\Delta V_{GND}$           | Difference in voltage between GND <sub>CP</sub> and GND (these pins should be connected together)          | -0.3        | +0.3                    | V    |

| P <sub>tot</sub>           | Total power dissipation                                                                                    |             | TBD                     | mW   |

| T <sub>stg</sub>           | Storage temperature                                                                                        | <b>-</b> 55 | +125                    | °C   |

| T <sub>amb</sub>           | Operating ambient temperature                                                                              | -30         | +85                     | °C   |

| T <sub>j</sub>             | Maximum junction temperature                                                                               |             | TBD                     | °C   |

# Handling

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

## Thermal characteristics

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |  |  |

|---------------------|---------------------------------------------------------|-------|------|--|--|

| R <sub>th j–a</sub> | Thermal resistance from junction to ambient in free air | 135   | K/W  |  |  |

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

#### **FUNCTIONAL DESCRIPTION**

#### Main Fractional-N divider

The RFin input (pins 5 and 6) drive a pre-amplifier to provide the clock to the first divider stage. For single ended operation, the signal should be fed to one of the inputs while the other one is AC grounded. The pre-amplifier has a high input impedance, dominated by pin and pad capacitance. The circuit operates with signal levels from –18dBm to +0dBm, and at frequencies as high as 2.5 GHz. The divider consists of a fully programmable bipolar prescaler followed by a CMOS counter. Divide ratios (512 to 65536) allow a minimum phase comparison frequency of 25kHz at 2.5 GHz RF.

At the completion of a main divider cycle, a main divider output pulse is generated which will drive the main phase comparator. Also, the fractional accumulator is incremented by the value of NF. The accumulator works with modulo Q set by FMOD. When the accumulator overflows the overall division ratio N will be increased by 1 to N + 1, the average division ratio over Q main divider cycles (either 5 or 8) will be

$$Nfrac = N + \frac{NF}{Q}$$

The output of the main divider will be modulated with a fractional phase ripple. The phase ripple is proportional to the contents of the fractional accumulator and is nulled by the fractional compensation charge pump.

The reloading of a new programming word is synchronized to the state of the main divider to avoid introducing a phase disturbance.

## **Auxiliary divider**

The auxiliary divider consists of a divider with fully programmable values between 128 and 16384. The AUXin input, pin 13, drives a pre-amplifier to provide the clock to the first divider stage. The AUXin negative input is internally connected to ground. The pre-amplifier has a high input impedance, dominated by pin and pad capacitance. The circuit operates with signal levels from –18dBm to +0dBm (80 to 636 mVpp), and at frequencies as high as 550 MHz. The divider consists of a fully programmable bipolar prescaler followed by a CMOS counter. The divide ratios allow a minimum phase comparison frequency of 25kHz at 550 MHz RF.

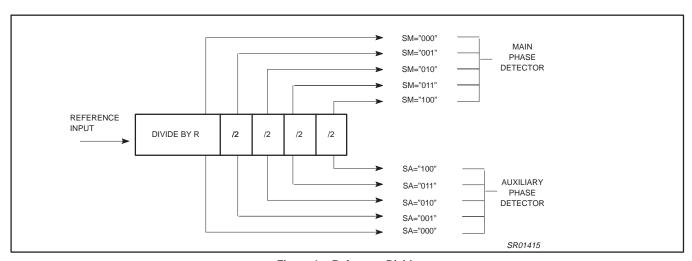

### Reference divider

The reference divider consists of a divider with programmable values between 4 and 1023 followed by a three bit binary counter. The 3 bit SM (SA) register (see figure 4) determines which fo the 5 output pulses are selected as the main (auxiliary) phase detector input.

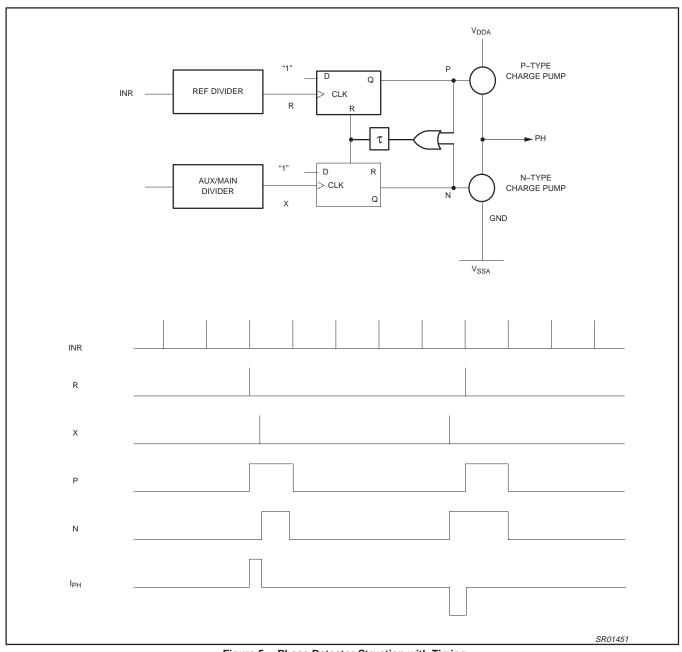

### Phase detector

The reference and main (aux) divider outputs are connected to a phase/frequency detector that controls the charge pump. The pump current is set by a an external resistor. The dead zone (caused by finite time taken to switch the current sources on or off) is cancelled by forcing the pumps ON for a minimum time at every cycle (backlash time) providing improved linearity.

Figure 4. Reference Divider

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

Figure 5. Phase Detector Struction with Timing

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

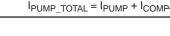

# Main Output Charge Pumps and Fractional **Compensation Currents.**

The main charge pumps on pins PHP and PHI are driven by the main phase detector and the charge pump current values are determined by the current at pin RSET. The fractional compensation is derived from the current at RSET, the contents of the fractional accumulator FRD and by the program value of the FDAC. The timing for the fractional compensation is derived from the main divider. See table of charge pump ratios.

# **Principle of Fractional Compensation**

The fractional compensation is designed into the circuit as a means of reducing or eliminating fractional spurs that predominate when the accumulator rolls over and the main divider counts one extra RF input cycle (+1, swallows a cycle). Since I<sub>COMP</sub> is the compensation current and I<sub>PUMP</sub> is the pump current, for each charge pump,

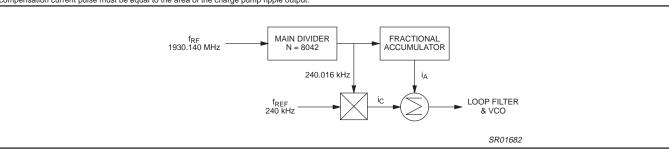

The theoretical values for FDAC are: 128 for FMOD = 1 (modulo 5) and 80 for FMOD = 0 (modulo 8). Fractional division will cause the pump to output a charge that is compensated for in order to reduce fractional spurs. This compensation is done by sourcing a small current, i<sub>A</sub>, see Figure 7, that is proportional to the fractional error phase. Figure 6 shows that for proper fractional compensation, the area of the fractional compensation current pulse must be equal to the area of the charge pump ripple.

This means  $I_{PUMP}^*Q=I_{COMP}^*128$ , where Q equals fractional-N modulus e.g., 2/5 for NF = 2 and FMOD = 1. The fractional compensation current is derived from the main charge pump in that it follows all the current scaling through external resistor setting, RN, programming or speed-up operation. For a given pump,

$I_{COMP} = (I_{PUMP} / 128) * (FDAC / 5*128) * FRD$

FRD is the fractional accumulator value.

Figure 6. Waveforms for NF = 2, Fraction = 0.4

Fig 6. shows that for a proper fractional compensation, the area of the fractional compensation current pulse must be equal to the area of the charge pump ripple output.

Figure 7. Current Injection Concept

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

## **Auxiliary Output Charge Pumps**

The auxiliary charge pumps on pin PHA are driven by the auxiliary phase detector and the current value is determined by the external resistor attached to pin R<sub>set</sub>.

### Main and auxiliary chargepump currents

| CP1 | CP0 | I <sub>PHA</sub> | I <sub>PHP</sub> | I <sub>PHP-SU</sub> | I <sub>PHI</sub> |

|-----|-----|------------------|------------------|---------------------|------------------|

| 0   | 0   | 1.5xlset         | 3xlset           | 15xlset             | 36xlset          |

| 0   | 1   | 0.5xlset         | 1xlset           | 5xlset              | 12xlset          |

| 1   | 0   | 1.5xlset         | 3xlset           | 15xlset             | 0                |

| 1   | 1   | 0.5xlset         | 1xlset           | 5xlset              | 0                |

#### NOTES

- 1.  $I_{SET} = \frac{V_{Set}}{R_{Set}}$ : bias current for charge pumps.

- 2. CP1 is used to disable the PHI pump, I<sub>PHP\_SU</sub> is the total current at pin PHP during speed up condition.

### **Lock Detect**

The output LOCK maintains a logic '1' when the auxiliary phase detector ANDed with the main phase detector indicates a lock condition. The lock condition for the main and auxiliary synthesizers is defined as a phase difference of less than  $\pm 1$  period of the frequency at the input  $\text{REF}_{\text{in+},-}$ . One counter can fulfill the lock condition when the other counter is powered down. Out of lock (logic '0') is indicated when both counters are powered down.

### Power-down mode

The power-down signal can be either hardware (PON) or software (PD). The PON signal is exclusively ORed with the PD bits. If PON = 0, then the part is powered up when PD = 1. PON can be used to invert the polarity of the software bit PD. When the synthesizer is reactivated after the power-down the main and reference dividers are synchronized to avoid possibility of random phase errors on power-up.

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

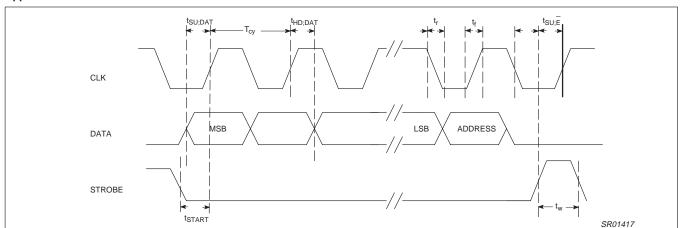

## Serial programming bus

The serial input is a 3-wire input (CLOCK, STROBE, DATA) to program all counter divide ratios, fractional compensation DAC, selection and enable bits. The programming data is structured into 24 bit words; each word includes 2 address bits. Figure 8 shows the timing diagram of the serial input. When the STROBE goes active HIGH, the clock is disabled and the data in the shift register remains unchanged. Depending on the 2 address bits the data is latched into

different working registers or temporary registers. In order to fully program the synthesizer, 3 words must be sent: C, B, and A. Table 1 shows the format and the contents of each word. The D word is for testing purposes only. The data for the fractional compensation DAC, FC is stored by the B word in temporary registers. When the A word is loaded, the data of these temporary registers is loaded together with the main divider ratio.

## Serial bus timing characteristics. See Figure 8.

$V_{DD} = V_{DDCP} = +3.0V$ ;  $T_{amb} = +25^{\circ}C$  unless otherwise specified.

| SYMBOL              | PARAMETER                             | MIN.    | TYP. | MAX. | UNIT |  |  |  |  |  |  |

|---------------------|---------------------------------------|---------|------|------|------|--|--|--|--|--|--|

| Serial programm     | ning clock; CLK                       | •       | •    |      | •    |  |  |  |  |  |  |

| t <sub>r</sub>      | Input rise time                       | _       | 10   | 40   | ns   |  |  |  |  |  |  |

| t <sub>f</sub>      | Input fall time                       | _       | 10   | 40   | ns   |  |  |  |  |  |  |

| T <sub>cy</sub>     | Clock period                          | 100     | _    | _    | ns   |  |  |  |  |  |  |

| Enable program      | Enable programming; STROBE            |         |      |      |      |  |  |  |  |  |  |

| t <sub>START</sub>  | Delay to rising clock edge            | 40      | _    | _    | ns   |  |  |  |  |  |  |

| t <sub>W</sub>      | Minimum inactive pulse width          | 1/fcomp | _    | _    | ns   |  |  |  |  |  |  |

| T <sub>SU;E</sub>   | Enable set-up time to next clock edge | 20      | _    | _    | ns   |  |  |  |  |  |  |

| Register serial in  | nput data; DATA                       |         |      |      |      |  |  |  |  |  |  |

| t <sub>SU;DAT</sub> | Input data to clock set-up time       | 20      | _    | _    | ns   |  |  |  |  |  |  |

| t <sub>HD;DAT</sub> | Input data to clock hold time         | 20      | _    | _    | ns   |  |  |  |  |  |  |

### **Application information**

Figure 8. Serial Bus Timing Diagram

# 2.5GHz low voltage fractional-N dual synthesizer

SA8026

# **Data format**

# Table 1. Format of programmed data

|   | LAST IN |     | MSB | · · | SERIAL PROGRA | MMING FORMAT |    | FIRST IN LSB |

|---|---------|-----|-----|-----|---------------|--------------|----|--------------|

| Γ | p23     | p22 | p21 | p20 | /             | /            | p1 | р0           |

# Table 2. A word, length 24 bits

| LAST                                         | · IN                                                                  |         |       |     |       | MSB                                                               |     |     |     |     |     |    |      |    |    |    |    |    |    |    | LSB | FIR | ST IN |

|----------------------------------------------|-----------------------------------------------------------------------|---------|-------|-----|-------|-------------------------------------------------------------------|-----|-----|-----|-----|-----|----|------|----|----|----|----|----|----|----|-----|-----|-------|

| Address fmod Fractional-N Main Divider ratio |                                                                       |         |       |     |       |                                                                   |     |     |     |     |     | Sp | oare |    |    |    |    |    |    |    |     |     |       |

| 0                                            | 0                                                                     | FM      | NF2   | NF1 | NF0   | N15                                                               | N14 | N13 | N12 | N11 | N10 | N9 | N8   | N7 | N6 | N5 | N4 | N3 | N2 | N1 | N0  | SK1 | SK2   |

| Defa                                         | ault:                                                                 | 0       | 0     | 1   | 0     | 0                                                                 | 0   | 1   | 0   | 0   | 0   | 1  | 0    | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0   | 0   | 0     |

| A wor                                        | d sele                                                                | ct      |       |     | Fixed | to 00.                                                            |     |     |     |     |     |    |      |    |    |    |    |    |    |    |     |     |       |

| Fracti                                       | onal N                                                                | 1odulus | selec | t   | FM 0  | FM 0 = modulo 8, 1 = modulo 5.                                    |     |     |     |     |     |    |      |    |    |    |    |    |    |    |     |     |       |

| Fracti                                       | Fractional-N Increment NF20 Fractional N Increment values 000 to 111. |         |       |     |       |                                                                   |     |     |     |     |     |    |      |    |    |    |    |    |    |    |     |     |       |

| N-Div                                        | N-Divider NoI                                                         |         |       |     | N0N   | 0N15, Main divider values 512 to 65535 allowed for divider ratio. |     |     |     |     |     |    |      |    |    |    |    |    |    |    |     |     |       |

# Table 3. B word, length 24 bits

| ADDR                                                                                                                                                                                               | ESS                     |    |     | F     | REFE                                                                                                                              | RENC                                                                             | E DI\ | /IDEF | ₹      |     |         | LO      | СК      | P      | D   |     | FRAC | oush/pull). open drain). dicator is low. in = 0 to power down. |     |     |     |     |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------|-------|--------|-----|---------|---------|---------|--------|-----|-----|------|----------------------------------------------------------------|-----|-----|-----|-----|-----|

| 0                                                                                                                                                                                                  | 1                       | R9 | R8  | R7    | R6                                                                                                                                | R5                                                                               | R4    | R3    | R2     | R1  | R0      | L1      | L0      | Main   | Aux | FC7 | FC6  | FC5                                                            | FC4 | FC3 | FC2 | FC1 | FC0 |

| Defa                                                                                                                                                                                               | ult:                    | 0  | 0   | 0     | 1                                                                                                                                 | 0                                                                                | 1     | 0     | 0      | 0   | 1       | 0       | 0       | 1      | 1   | 0   | 1    | 0                                                              | 1   | 0   | 0   | 0   | 0   |

| B word                                                                                                                                                                                             | word select Fixed to 01 |    |     |       |                                                                                                                                   |                                                                                  |       |       |        |     |         |         |         |        |     |     |      |                                                                |     |     |     |     |     |

| R-Divider                                                                                                                                                                                          |                         |    | R0F | R9, R | efere                                                                                                                             | nce di                                                                           | vider | value | s 4 to | 102 | 3 allov | wed for | divider | ration |     |     |      |                                                                |     |     |     |     |     |

| Lock detect output                                                                                                                                                                                 |                         |    |     |       | 0 0<br>0 1<br>1 0<br>1 1                                                                                                          | 0 1 Combined main, aux, lock detect signal present at the LOCK pin (open drain). |       |       |        |     |         |         |         |        |     |     |      |                                                                |     |     |     |     |     |

| Power down  Main = 1: power to N-divider, reference divider, main charge pumps, Main = 0 to power down.  Aux = 1: power to Aux divider, reference divider, aux charge pump, Aux = 0 to power down. |                         |    |     |       |                                                                                                                                   |                                                                                  |       |       |        |     |         |         |         |        |     |     |      |                                                                |     |     |     |     |     |

| Fractio                                                                                                                                                                                            | Fractional Compensation |    |     | n     | FC70 Fractional Compensation charge pump current DAC, values 0 to 255. Recommended values: FC = 80 for MOD 8; FC = 128 for MOD 5. |                                                                                  |       |       |        |     |         |         |         |        |     |     |      |                                                                |     |     |     |     |     |

# Table 4. C word, length 24 bits

| Addı          | ress      |                                                            |                                                                         |     |             |                                                                         | Auxi | liary | Divid | ler |    |    |    |    |    | С   | Р   |     | SM  |     |     | SA  |     |

|---------------|-----------|------------------------------------------------------------|-------------------------------------------------------------------------|-----|-------------|-------------------------------------------------------------------------|------|-------|-------|-----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1             | 0         | A13                                                        | A12                                                                     | A11 | A10         | A9                                                                      | A8   | A7    | A6    | A5  | A4 | А3 | A2 | A1 | A0 | CP1 | CP0 | SM2 | SM1 | SM0 | SA2 | SA1 | SA0 |

| Default 0 0 0 |           |                                                            | 0                                                                       | 0   | 0           | 1                                                                       | 1    | 1     | 0     | 0   | 1  | 0  | 1  | 0  | 1  | 1   | 0   | 0   | 0   | 0   | 0   | 0   |     |

| C word select |           |                                                            |                                                                         |     | Fixed to 10 |                                                                         |      |       |       |     |    |    |    |    |    |     |     |     |     |     |     |     |     |

| A-Divi        | A-Divider |                                                            |                                                                         |     |             | A0A13, Auxiliary divider values 128 to 16384 allowed for divider ratio. |      |       |       |     |    |    |    |    |    |     |     |     |     |     |     |     |     |

| Charg         | e pum     | tio                                                        | CP1, CP0: Charge pump current ratio, see table of charge pump currents. |     |             |                                                                         |      |       |       |     |    |    |    |    |    |     |     |     |     |     |     |     |     |

| Main o        |           | SM comparison divider select for main phase detector.      |                                                                         |     |             |                                                                         |      |       |       |     |    |    |    |    |    |     |     |     |     |     |     |     |     |

| Aux co        |           | SA Comparison divider select for auxiliary phase detector. |                                                                         |     |             |                                                                         |      |       |       |     |    |    |    |    |    |     |     |     |     |     |     |     |     |

# Table 5. D word, length 24 bits

| ΑI   | DDRE   | SS    | S | YNTH | ESIZE<br>BITS | R TES | ST |                    |   |   |   |   |   | SYN | THESI | ZER 1   | rest | BITS |   |   |   |   |   |

|------|--------|-------|---|------|---------------|-------|----|--------------------|---|---|---|---|---|-----|-------|---------|------|------|---|---|---|---|---|

| 1    | 1      | 0     | _ | _    | _             | -     | _  | Tspu               | _ | _ | _ | _ | _ | -   | _     | _       | _    | _    | _ | _ | _ | _ | - |

| DI   | EFAU   | LT    | 0 | 0    | 0             | 0     | 0  | 0                  | 0 | 0 | 0 | 0 | 0 | 0   | 0     | 0       | 0    | 0    | 0 | 0 | 0 | 0 | 0 |

| Tspu | ı: Spe | ed up |   |      |               |       |    | synthe<br>test bit |   |   |   |   |   |     |       | the tim | ne.  |      |   |   |   |   |   |

# 2.5GHz low voltage dual fractional-N frequency synthesizer

SA8026

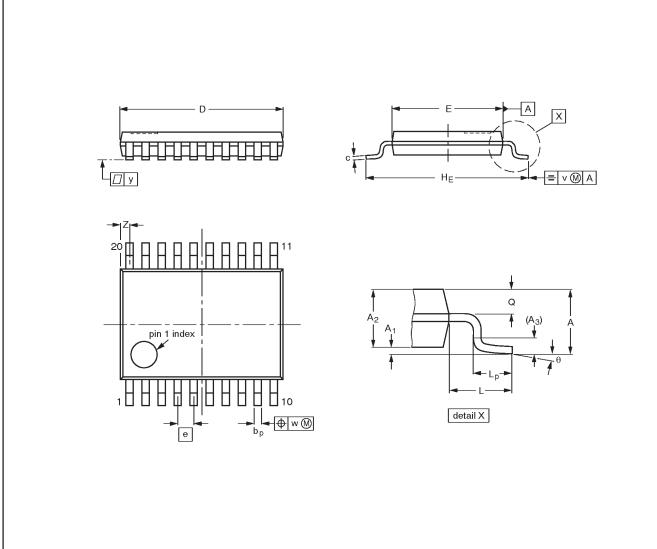

TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm

SOT360-1

# DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | Α1           | A <sub>2</sub> | <b>A</b> <sub>3</sub> | рb           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L   | Lp           | Œ          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|--------------|----------------|-----------------------|--------------|------------|------------------|------------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05 | 0.95<br>0.80   | 0.25                  | 0.30<br>0.19 | 0.2<br>0.1 | 6.6<br>6.4       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.5<br>0.2       | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | RENCES | EUROPEAN   | ICCUE DATE                       |  |

|----------|-----|----------|--------|------------|----------------------------------|--|

| VERSION  | IEC | JEDEC    | EIAJ   | PROJECTION | ISSUE DATE                       |  |

| SOT360-1 |     | MO-153AC |        |            | <del>-93-06-16</del><br>95-02-04 |  |

# 2.5GHz low voltage dual fractional—N frequency synthesizer

SA8026

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                            |

|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                         |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### Definitions

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

Let's make things better.

Philips Semiconductors